Distributed by:

# www.Jameco.com + 1-800-831-4242

The content and copyrights of the attached material are the property of its owner.

3501 ED BLUESTEIN BLVD., AUSTIN, TEXAS 78721

## **Advance Information**

## Jameco Part Number 25355

### MC68701 MICROCOMPUTER UNIT (MCU)

The MC68701 is an 8-bit single chip microcomputer unit (MCU) which significantly enhances the capabilities of the M6800 family of parts. It can be used in production systems to allow for easy firmware chances with minimum delay or it can be used to emulate the MC6801/03 To software development. It includes an upgraded M6800 microprocessor unit (MPU) with upward source and object code compatibility. Execution times of key instructions have been improved and several new instructions have been added including an unsigned multiply. The MCU can function as a monolithic microcomputer or can be expanded to a 64K byte address space. It is TTL compatible and requires one +5 volt power supply for nonprogramming operation. An additional Vpp power supply is needed for EPROM programming. On-chip resources include 2048 bytes of EPROM, 128 bytes of RAM, Serial Communications Interface (SCI), parallel I/O, and a three function Programmable Timer. A summary of MCU features includes:

- Enhanced MC6800 Instruction Set

- 8 × 8 Multiply Instruction

- Serial Communications Interface (SCI)

- Upward Source and Object Code Compatibility with the MC6800

- 16-Bit Three-Function Programmable Timer

- Single-Chip or Expanded Operation to 64K Byte Address Space

- Bus Compatibility with the M6800 Family

- 2048 Bytes of UV Erasable, User Programmable ROM (EPROM)

- 128 Bytes of RAM (64 Bytes Retainable on Powerdown).

- 29 Parallel I/O and Two Handshake Control Lines

- Internal Clock Generator with Divide-by-Four Output

- −40 to 85°C Temperature Range

### GENERIC INFORMATION

| Package Type | Frequency (MHz) | Temperature    | Generic Number |

|--------------|-----------------|----------------|----------------|

| Ceramic      | 1.0             | 0°C to 70°C    | MC68701L       |

| L Suffix     | 1.0             | – 40°C to 85°C | MC68701CL      |

|              | 1.25            | 0°C to 70°C    | MC68701L-1     |

|              | 1.25            | – 40°C to 85°C | MC68701CL-1    |

|              | 1.5             | 0°C to 70°C    | MC68A701L      |

|              | 2.0             | 0°C to 70°C    | MC68B701L      |

## MC68701

## MOS

(N-CHANNEL, SILICON-GATE, DEPLETION LOAD)

MICROCOMPUTER WITH EPROM

### PIN ASSIGNMENT

| ∨ss <b>ū</b> ⊨ ● ` | <b>→</b> 40 <b>1</b> E |

|--------------------|------------------------|

| XTAL1 🗖 2          | 39 <b>II SC</b> 1      |

| EXTAL 2 🛛 3        | 38 <b>∏</b> SC2        |

| NMI 0 4            | 37 <b>2 P30</b>        |

| <b>iRQ1 □</b> 5    | 36 P31                 |

| RESET/VPP06        | 35 P32                 |

| <b>∨cc[</b> 7      | 34 <b>1</b> P33        |

| P20 <b>[</b> 8     | 33 <b>🗖 P34</b>        |

| <b>P21 □</b> 9     | 32 <b>1</b> P35        |

| P22 🕻 10           | 31 <b>2 P36</b>        |

| P23 🛘 11           | 30 <b>1</b> P37        |

| P <b>24</b> 🛘 12   | 29 <b>1 P40</b>        |

| P10 <b>[</b> 13    | 28 <b>1</b> P41        |

| P11 <b>[</b> 14    | 27 <b>7 P42</b>        |

| P1 2 🖸 15          | 26 <b>7 P43</b>        |

| P13 <b>0</b> 16    | 25 <b>1 P44</b>        |

| P14 <b>[</b> 17    | 24 <b>1 P45</b>        |

| P15 <b>[</b> 18    | 23 <b>1</b> P46        |

| <b>P16 [</b> 19    | 22 <b>] P47</b>        |

| P17 🖸 20           | 21 <b>2 Vcc</b>        |

|                    | Standby                |

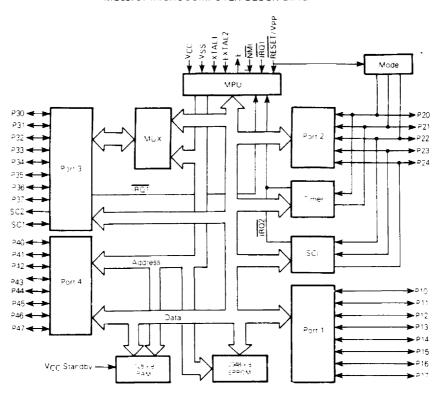

#### MC68701 MICROCOMPUTER BLOCK DIAGRAM

#### MAXIMUM RATINGS

| Rating                                             | Symbol          | Value                                                     | Unit |

|----------------------------------------------------|-----------------|-----------------------------------------------------------|------|

| Supply Voltage                                     | Vcc             | -0.3 to $+7.0$                                            | V    |

| Input Voltage                                      | V <sub>in</sub> | -0.3 to $+7.0$                                            | V    |

| Operating Temperature Range<br>MC68701<br>MC68701C | ТД              | T <sub>L</sub> to T <sub>H</sub><br>0 to 70<br>– 40 to 85 | °C   |

| Storage Temperature Range                          | Tstg            | 0 to 85                                                   | эC   |

THERMAL CHARACTERISTICS

| Characteristic     | Symbol | Value | Rating |

|--------------------|--------|-------|--------|

| Thermal Resistance | A . A  | 50    | °C/W   |

| Ceramic Package    | #JA    |       |        |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages. to this high-impedance circuit. For proper operation it is recommended that Vin and Vout be constrained to the range  $V_{SS} \le (V_{in} \text{ or } V_{out}) \le V_{CC}$ . Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (e.g., either VSS or VCC).

(1)

## **POWER CONSIDERATIONS**

The average chip-junction temperature, TJ, in °C can be obtained from:

$$T_{J} = T_{A} + (P_{D} \bullet \theta_{JA})$$

Where:

TA = Ambient Temperature, °C

θ JA = Package Thermal Resistance, Junction-to-Ambient, °C/W

PD = PINT + PPORT

PINT=ICC × VCC, Watts - Chip Internal Power

PPORT = Port Power Dissipation, Watts - User Determined

For most applications PPORT

PINT and can be neglected. PPORT may become significant if the device is configured to drive Darlington bases or sink LED loads.

An approximate relationship between PD and TJ (if PPORT is neglected) is:

$$P_D = K + (T_J + 273 ^{\circ}C)$$

(2)

Solving equations 1 and 2 for K gives:  $K = PD \bullet (TA + 273 °C) + \theta JA \bullet PD^2$

for a known TA. Using this value of K the values of PD and TJ can be obtained by solving equations (1) and (2) iteratively for any value of TA.

CONTROL TIMING ( $V_{CC} = 5.0 \text{ V } \pm 5\%$ ,  $V_{SS} = 0$ ,  $T_A = 0$  to 70 °C)

| Characteristic                   | Cbl             | MCE | C68701 N |     | MC68701-1 |     | MC68A701 |     | MC68B701 |      |

|----------------------------------|-----------------|-----|----------|-----|-----------|-----|----------|-----|----------|------|

| Citalacteristic                  | Symbol          | Min | Max      | Min | Max       | Min | Max      | Min | Max      | Unit |

| Frequency of Operation           | fo              | 0.5 | 1.0      | 0.5 | 1.25      | 0.5 | 15       | 0.5 | 2.0      | MHz  |

| Crystal Frequency                | fXTAL           | 2.0 | 4.0      | 2.0 | 5.0       | 2.0 | 6.0      | 2.0 | 8.0      | MHz  |

| External Oscillator Frequency    | 4f <sub>O</sub> | 2.0 | 4.0      | 2.0 | 5.0       | 2.0 | 6.0      | 2.0 | 8.0      | MHz  |

| Crystal Oscillator Start Up Time | trc             | _   | 100      | _   | 100       |     | 100      | -   | 100      | ms   |

| Processor Control Setup Time     | tPCS            | 200 | -        | 170 | -         | 140 | -        | 110 |          | ns   |

## DC ELECTRICAL CHARACTERISTICS ( $V_{CC} = 5.0 \text{ Vdc} \pm 5\%$ , $V_{SS} = 0$ , $T_A = T_L$ to $T_H$ , unless otherwise noted)

|                                                                                                          |                                        |                  |                                                | MC68701           |                                              | 1                                              |            |                                            |      |

|----------------------------------------------------------------------------------------------------------|----------------------------------------|------------------|------------------------------------------------|-------------------|----------------------------------------------|------------------------------------------------|------------|--------------------------------------------|------|

| Characteristic                                                                                           |                                        | Symbol           | Min                                            | Тур               | Max                                          | Min                                            | Тур        | Max                                        | Unit |

| Input High Voltage                                                                                       | RESET Other Inputs*                    | V <sub>1H</sub>  | V <sub>SS</sub> +4.0<br>V <sub>SS</sub> +2.0   | 1 1               | Vcc<br>Vcc                                   | V <sub>SS</sub> +4.0<br>V <sub>SS</sub> +2.2   | -          | Vcc<br>Vcc                                 | V    |

| Input Low Voltage                                                                                        | RESET<br>Other Inputs*                 | VIL              | V <sub>SS</sub> = 0.3<br>V <sub>SS</sub> = 0.3 | _                 | V <sub>SS</sub> +0.4<br>V <sub>SS</sub> +0.8 | V <sub>SS</sub> = 0.3<br>V <sub>SS</sub> = 0.3 | -          | V <sub>SS</sub> +04<br>V <sub>SS</sub> +08 | V    |

| Input Current, See Note<br>(V <sub>in</sub> = 0 to 2.4 V)                                                | Port 4<br>SCI                          | <sup>‡</sup> in  | _<br>_                                         | _<br>_            | 0.6<br>1.0                                   | _<br>_                                         | -          | 1 0<br>1 6                                 | mΑ   |

| Input Current (V <sub>in</sub> = 0 to 5.25 V)                                                            | NMI, IRQ1                              | lin              | -                                              | 15                | 2.5                                          | _                                              | 15         | 5                                          | μА   |

| Input Current<br>(V <sub>in</sub> = 0 to 0.4 V)<br>(V <sub>in</sub> = 4.0 V to V <sub>CC</sub> )         | RESET/Vpp                              | l <sub>in</sub>  | _                                              | - 2.0<br>-        | _<br>8.0                                     | _<br>_<br>_                                    | - 2.0<br>- | 8 0                                        | mΑ   |

| Hi-Z (Off State) Input Current (Vin = 0.5 to 2.4 V)                                                      | Ports 1, 2, and 3                      | <sup> </sup> TSI | _                                              | 2                 | 10                                           | _                                              | 2          | 20                                         | μΑ   |

| Output High Voltage<br>$(I_{Load} = -65 \mu A, V_{CC} = Min)$<br>$(I_{Load} = -100 \mu A, V_{CC} = Min)$ | Port 4, SC1, SC2<br>Other Outputs      | ∨он              | V <sub>SS</sub> +2.4<br>V <sub>SS</sub> +2.4   | <del>-</del><br>- | <u>-</u><br>-                                | V <sub>SS</sub> +2.4<br>V <sub>SS</sub> +2.4   | <u>-</u>   | -<br>+                                     | V    |

| Output Low Voltage ILoad = 2.0 mA, VCC = Min)                                                            | All Outputs                            | VOL              | -                                              | _                 | V <sub>SS</sub> +0.5                         | -                                              | _          | V <sub>SS</sub> +0.6                       | V    |

| Darlington Drive Current (V <sub>O</sub> = 1.5 V)                                                        | Port 1                                 | <sup>1</sup> ОН  | 1.0                                            | 2.5               | 10.0                                         | 1.0                                            | 2.5        | 10.0                                       | mA   |

| Internal Power Dissipation (Measured at TA = TL in Steady                                                | -State Operation)                      | PINT             | _                                              | -                 | 1500                                         | sinde                                          | _          | 1500                                       | mW   |

| input Capacitance $(V_{in} = 0, T_A = 25^{\circ}C, f_O = 1 \text{ MHz})$                                 | Port 3,<br>Port 4, SCI<br>Other Inputs | Cin              | _<br>_                                         | -<br>-            | 12.5<br>10.0                                 |                                                | _          | 12.5<br>10.0                               | рF   |

| V <sub>CC</sub> Standby                                                                                  | Powerdown<br>Powerup                   | VSBB<br>VSB      | 4.0<br>4.75                                    | -<br>-            | 5.25<br>5.25                                 | 4.0<br>4.75                                    | -<br>-     | 5 25<br>5 25                               | V    |

| Standby Current                                                                                          | Powerdown                              | ISBB             | _                                              | _                 | 6.0                                          | -                                              |            | 8.0                                        | mΑ   |

| Programming Time Per Byte (TA =                                                                          | 25°C)                                  | tpp              | 25                                             | -                 | 50                                           | 25                                             | -          | 50                                         | ms   |

| Programming Voltage (T <sub>A</sub> = 25°C)                                                              |                                        | Vpp              | 20.0                                           | 21.0              | 22.0                                         | 20.0                                           | 21.0       | 22.0                                       | V    |

| Programming Current (VRESET = Vpp, $T_A = 25$ °C)                                                        | see Figure 15                          | Ірр              | -                                              | 30                | 50                                           | _                                              | 30         | 50                                         | mΑ   |

<sup>\*</sup>Except mode programming levels; see Figure 15.

NOTE: RESET/VPP I<sub>in</sub> differs from MC6801 and MC6803 values.

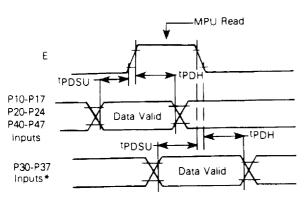

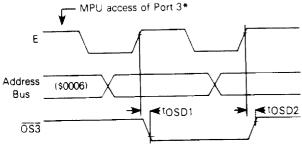

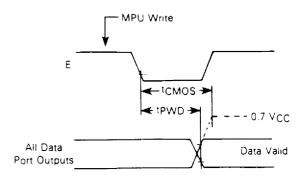

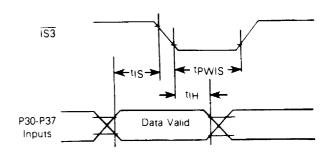

## PERIPHERAL PORT TIMING (Refer to Figures 3-6)

| Characteristics                                                         |                  | MC68701 |          | MC68701-1 |     | MC68A701 |     | MC68B701 |     | Unit |

|-------------------------------------------------------------------------|------------------|---------|----------|-----------|-----|----------|-----|----------|-----|------|

|                                                                         |                  | Min     | Max      | Min       | Max | Min      | Max | Min      | Max | Onn  |

| Peripheral Data Setup Time                                              | tPDSU            | 200     | _        | 200       | _   | 150      | _   | 100      | -   | ns   |

| Peripheral Data Hold Time                                               | <sup>t</sup> PDH | 200     | _        | 200       | -   | 150      | _   | 100      | 1   | ns   |

| Delay Time, Enable Positive Transition to OS3 Negative Transition       | tOSD1            | _       | 350      | _         | 350 | 1        | 300 | _        | 250 | ns   |

| Delay Time, Enable Positive Transition to OS3 Positive Transition       | tOSD2            | -       | 350      | -         | 350 | -        | 300 | _        | 250 | ns   |

| Delay Time, Enable Negative Transition to Peripheral Data Valid         | tPWD             |         | 350      | _         | 350 | 1        | 300 | -        | 250 | ns   |

| Delay Time, Enable Negative Transition to<br>Peripheral CMOS Data Valid | tcmos            | _       | 2.0      | ş         | 2.0 | 1        | 2.0 | _        | 2.0 | μS   |

| Input Strobe Pulse Width                                                | †PWIS            | 200     | -        | 200       | -   | 150      |     | 100      | _   | ns   |

| Input Data Hold Time                                                    | tін              | 50      | _        | 50        | _   | 40       | _   | 30       | _   | ns   |

| Input Data Setup Time                                                   | tIS              | 20      | <u> </u> | 20        | _   | 20       |     | 20       | _   | ns   |

# FIGURE 1 — DATA SETUP AND HOLD TIMES (MPU READ)

\* Port 3 Non-Latched Operation (LATCHE ENABLE = 0)

FIGURE 3 — PORT 3 OUTPUT STROBE TIMING (SINGLE-CHIP MODE)

\* Access matches Output Strobe Select (OSS = 0, a read; OSS = 1, a write)

FIGURE 2 — DATA SETUP AND HOLD TIMES (MPU WRITE)

NOTES:

- 1. 10 k Pullup resistor required for Port 2 to reach 0.7 VCC

- 2. Not applicable to P21

- 3. Port 4 cannot be pulled above VCC

FIGURE 4 — PORT 3 LATCH TIMING (SINGLE-CHIP MODE)

NOTE: Timing measurements are referenced to a low voltage of 0.8 volts and a high voltage of 2.0 volts unless otherwise noted.

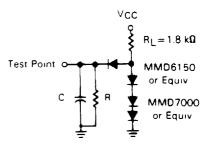

FIGURE 5 - CMOS LOAD

FIGURE 6 - TIMING TEST LOAD PORTS 1, 2, 3, 4

C = 90 pF for P30-P37, P40-P47, E, SC1, SC2 = 30 pF for P10-P17, P20-P24 R = 37 kΩ for P40-P47, SC1, SC2, = 24 kΩ for P10-P17, P20-P24, P30-P37, E

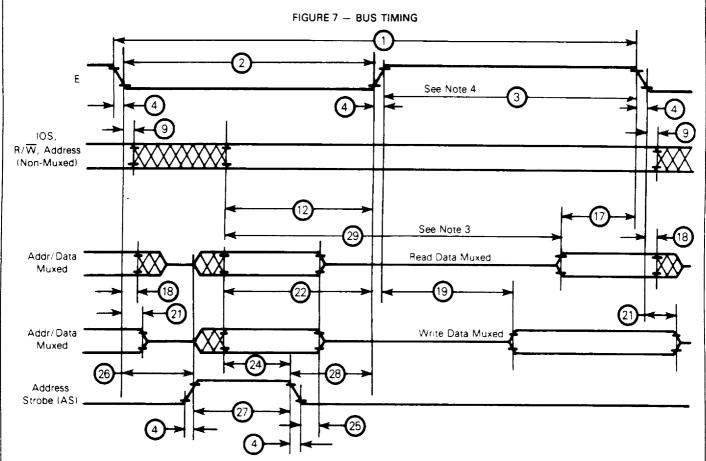

BUS TIMING (See Notes 2 and 3)

| Ident  | Characteristic                             | Sumbal              | MC68701 |      | MC68701-1 |      | MC68A701 |      | MC68B701 |      |      |

|--------|--------------------------------------------|---------------------|---------|------|-----------|------|----------|------|----------|------|------|

| Number |                                            | Symbol              | Min     | Max  | Min       | Max  | Min      | Max  | Min      | Max  | Unit |

| 1      | Cycle Time                                 | tcyc                | 1.0     | 2.0  | 0.8       | 2.0  | -        | 2.0  | 0.5      | 2.0  | μS   |

| 2      | Pulse Width, E Low                         | PWEL                | 430     | 1000 | 360       | 1000 | 300      | 1000 | 210      | 1000 | ns   |

| 3      | Pulse Width, E High                        | PWEH                | 450     | 1000 | 360       | 1000 | 300      | 1000 | 220      | 1000 | ns   |

| 4      | Clock Rise and Fall Time                   | t <sub>r</sub> , tf | -       | 25   | _         | 25   | _        | 25   |          | 20   | ns   |

| 9      | Address Hold Time                          | <sup>t</sup> AH     | 20      | _    | 20        | _    | 20       | _    | 10       |      | ns   |

| 12     | Non-Muxed Address Valid Time to E*         | tAV                 | 200     | _    | 150       | _    | 115      | -    | 70       | _    | ns   |

| 17     | Read Data Setup Time                       | tDSR                | 80      | _    | 70        | _    | 60       | _    | 40       | _    | ns   |

| 18     | Read Data Hold Time                        | <sup>†</sup> DHR    | 10      | _    | 10        | _    | 10       | -    | 10       |      | ns   |

| 19     | Write Data Delay Time                      | tDDW                | -       | 225  | -         | 200  | _        | 170  | -        | 120  | ns   |

| 21     | Write Data Hold Time                       | ₹DHW                | 20      | -    | 20        | _    | 20       | _    | 10       | _    | ns   |

| 22     | Multiplexed Address Valid Time to E Rise*  | tAVM                | 200     | _    | 150       | _    | 115      | _    | 80       | _    | ns   |

| 24     | Multiplexed Address Valid Time to AS Fall* | tASL                | 60      | _    | 50        | _    | 40       |      | 20       |      | ns   |

| 25     | Multiplexed Address Hold time              | †AHL                | 20      | _    | 20        | _    | 20       | _    | 10       |      | ns   |

| 26     | Delay Time, E to AS Rise*                  | <sup>†</sup> ASD    | 90**    |      | 70**      | _    | 60**     | _    | 45**     | -    | ns   |

| 27     | Pulse Width, AS High*                      | PWASH               | 220     | _    | 170       | -    | 140      | _    | 110      | _    | ns   |

| 28     | Delay Time, AS to E Rise*                  | †ASED               | 90      | _    | 70        | _    | 60       | -    | 45       |      | ns   |

| 29     | Usable Access Time*                        | tACC                | 595     | _    | 465       | _    | 380      | _    | 270      | _    | ns   |

<sup>\*</sup> At specified cycle time.

<sup>\*\*</sup>tASD parameters listed assume external TTL clock drive with 50% ±5% duty cycle. Devices driven by an external TTL clock with 50% ±1% duty cycle or which use a crystal have the following tASD specification: 100 nanoseconds minimum (1.0 MHz devices), 80 nanoseconds minimum (1.25 MHz devices), 65 nanoseconds minimum (1.5 MHz devices), 50 nanoseconds minimum (1.26 MHz devices), 65 nanoseconds minimum (1.27 MHz devices), 65 nanoseconds minimum (1.28 MHz

#### NOTES:

- 1. Voltage levels shown are V<sub>L</sub>≤0.5 V, V<sub>H</sub>≥2.4 V, unless otherwise specified.

- 2. Measurement points shown are 0.8 V and 2.0 V, unless otherwise specified.

- 3. Usable access time is computed by 12+3-17+4.

- 4. Memory devices should be enabled only during E high to avoid port 3 bus contention.

#### INTRODUCTION

The MC68701 is an 8-bit monolithic microcomputer which can be configured to function in a wide variety of applications. The facility which provides this extraordinary flexibility is its ability to be hardware programmed into eight different operating modes. The operating mode controls the configuration of 18 of the 40 MCU pins, available on-chip resources, memory map, location (internal or external) of interrupt vectors, and type of external bus. The configuration of the remaining 22 pins is not dependent on the operating mode.

Twenty-nine pins are organized as three 8-bit ports and one 5-bit port. Each port consists of at least a Data Register and a write-only Data Direction Register. The Data Direction Register is used to define whether corresponding bits in the Data Register are configured as an input (clear) or output (set).

The term "port," by itself, refers to all of the hardware associated with the port. When the port is used as a "data port" or "I/O port," it is controlled by the port Data Direction Register and the programmer has direct access to the port pins using the port Data Register. Port pins are labled as Pij where i identifies one of four ports and j indicates the particular bit.

The Microprocessor Unit (MPU) is an enhanced MC6800 MPU with additional capabilities and greater throughput. It is upward source and object code compatible with the

MC6800. The programming model is depicted in Figure 8 where Accumulator D is a concatenation of Accumulators A and B. A list of new operations added to the M6800 instruction set are shown in Table 1.

The basic difference between the MC6801 and the MC68701 is that the MC6801 has an onboard ROM while the MC68701 has an onboard EPROM. The MC68701 is pin and code compatible with the MC6801 and can be used to emulate the MC6801, allowing easy software development using the onboard EPROM. Software developed using the MC68701 can then be masked into the MC6801 ROM.

In order to support the onboard EPROM, the MC68701 differs from the MC6801 as follows:

- (1) Mode 0 in the MC6801 is a test mode only, while in the MC68701 Mode 0 is also used to program the onboard EPROM and has interrupt vectors at \$BFF0-\$BFFF rather than \$FFF0-\$FFFF.

- (2) The MC68701 RAM/EPROM Control Register has two bits used to control the EPROM in Mode 0 that are not defined in the MC6801 RAM Control Register.

- (3) The RESET/Vpp pin in the MC68701 is dual purpose, used to supply EPROM power as well as to reset the device; while in the MC6801 the pin is called RESET and is used only to reset the device.

8-Bit Accumulators A and B Or 16-Bit Double Accumulator D D Index Register (X) Х Stack Pointer (SP) SP Program Counter (PC) PC 0 Condition Code Register (CCR) Carry/Borrow from MSB Overflow Zero Negative Interrupt Half Carry (From Bit 3)

FIGURE 8 - MC68701/6801/6803 PROGRAMMING MODEL